计算机组成原理:CPU的结构与功能

计算机组成原理:CPU的结构与功能

一、CPU的基本功能

CPU 是计算机的“大脑”,其核心功能可概括为以下四个方面:

| 功能 | 说明 |

|---|---|

| 指令控制 | 按程序顺序取指、执行,实现程序流程控制(如跳转、循环、调用)。 |

| 操作控制 | 对指令进行译码,产生控制信号,协调ALU、寄存器、存储器等部件协同工作。 |

| 时间控制 | 通过时钟脉冲和机器周期,确保各操作在正确的时间节拍内完成。 |

| 数据加工 | 执行算术与逻辑运算(加减乘除、与或非),对数据进行处理和变换。 |

二、CPU的组成

现代CPU主要由以下四个部分构成:

运算器(ALU) :负责数据运算

控制器(CU) :负责指令控制与协调

寄存器组:高速暂存单元,存放指令、数据、地址、状态

内部总线:连接各部件的数据通路

CPU与主存构成“主机”,I/O设备与辅助存储器构成“外设”。CPU通过总线与主存通信。

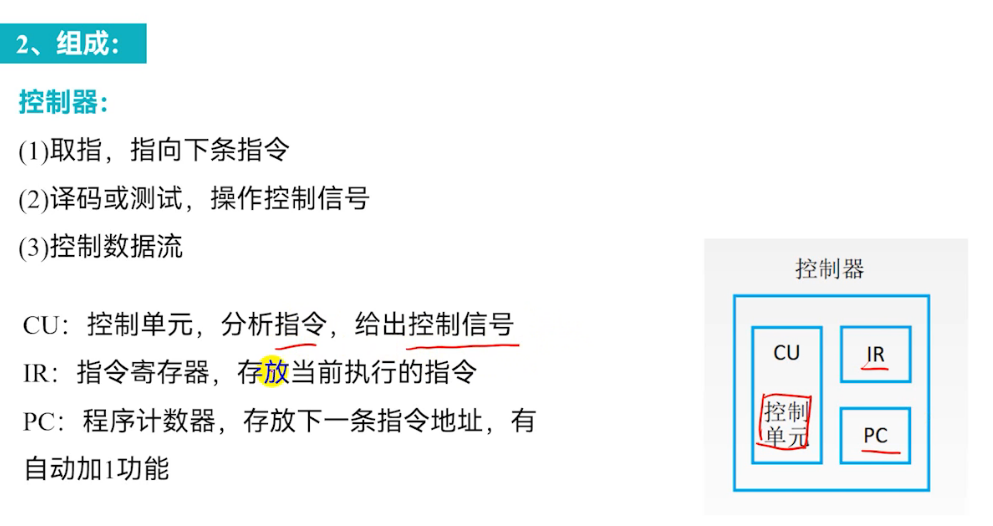

三、控制器详解

(1)控制器的功能

控制器是CPU的“指挥中心”,主要完成:

① 取指:从内存中取出下一条指令,送入IR,并更新PC(PC自动+1)

② 译码:分析指令的操作码和地址码,确定操作类型和操作数来源

③ 控制数据流:根据译码结果,发出控制信号,协调ALU、寄存器、存储器等部件工作

(2)关键寄存器说明

CU(Control Unit) :控制单元,负责生成控制信号。

IR(Instruction Register) :指令寄存器,存放当前正在执行的指令。

PC(Program Counter) :程序计数器,存放下一条指令的地址,每次取指后自动加1。

四、运算器详解

(1)运算器的功能

运算器(又称ALU)是CPU中执行算术运算和逻辑运算的核心部件:

- 算术运算:加、减、乘、除、移位等

- 逻辑运算:与、或、非、异或等

(2)关键寄存器说明

- ACC(Accumulator) :累加器,常用于存放运算中间结果或最终结果。

- MQ(Multiplier-Quotient Register) :乘商寄存器,在乘法中存放乘数/被乘数,在除法中存放商。

- X:通用操作数寄存器,可存放任意操作数。

- ALU(Arithmetic Logic Unit) :算术逻辑单元,内部由加法器、移位器、逻辑门电路组成,完成所有运算。

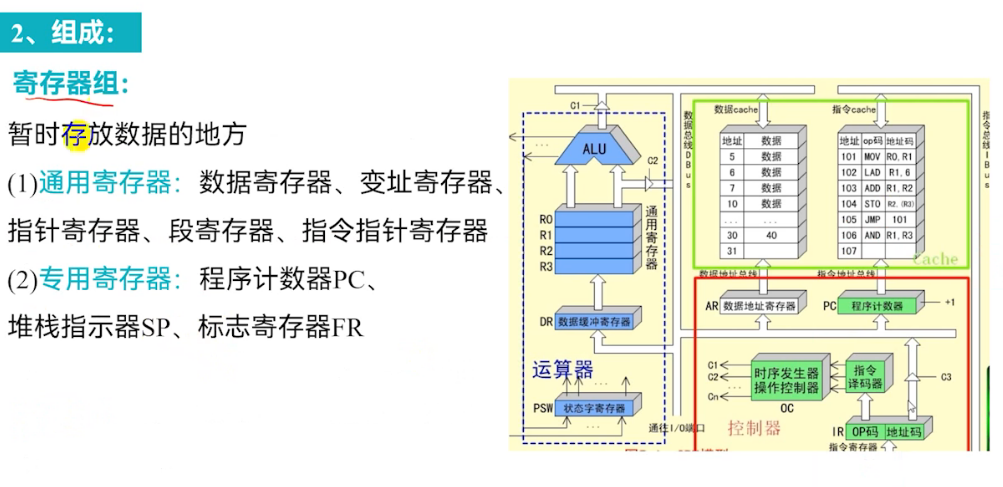

五、寄存器组详解

(1)寄存器组的作用

寄存器组是CPU内部的高速存储单元,用于暂时存放数据、地址、指令、状态标志,是CPU与主存之间数据交换的缓冲区。

该图展示了一个较完整的CPU内部结构,包括:

左侧:运算器(ALU + 通用寄存器 R0~R3 + DR + PSW)

右上:数据Cache / 指令Cache

右下:控制器(CU + IR + PC + OC)

总线系统:数据总线、地址总线、控制总线

(2)寄存器分类

① 通用寄存器(General Purpose Registers)

用途灵活,可用于存放数据、地址、中间结果。

包括:

- 数据寄存器(如AX, BX, CX, DX)

- 变址寄存器(如SI, DI)

- 指针寄存器(如SP, BP)

- 段寄存器(如CS, DS, ES)

- 指令指针寄存器(IP/EIP,即PC)

② 专用寄存器(Special Purpose Registers)

功能固定,不可随意改写。

包括:

- PC(程序计数器) :指向下一条指令地址,自动+1。

- SP(堆栈指针) :指向当前栈顶。

- FR(标志寄存器 / PSW) :记录运算结果的状态标志(如CF进位、ZF零、SF符号、OF溢出等)。

六、指令周期

1. 指令周期的基本概念

指令周期:CPU从取指到执行完成一条指令所花费的总时间。

基本划分(最简模型):

-

取指周期(Fetch Cycle) :取指令 + 分析指令(译码)

-

执行周期(Execute Cycle) :执行指令操作(如运算、访存、跳转等)

2. 完整指令周期的四个阶段

一个完整的指令周期可能包含以下四个阶段(并非所有指令都经历全部阶段):

| 阶段 | 功能说明 | 是否必需 |

|---|---|---|

| 取指周期 | 从内存取出指令,送入IR;PC自动+1 | ✅ 必需 |

| 间址周期 | 若为间接寻址,需根据指令地址再取一次有效地址 | ❌ 可选 |

| 执行周期 | 执行指令操作(算术、逻辑、访存、跳转等) | ✅ 必需 |

| 中断周期 | 检查是否有中断请求,若有则保存现场、转入ISR | ❌ 可选 |

⚠️ 注意:

“间址周期”只在间接寻址指令中出现(如 MOV AX, [BX] 是直接寻址,无间址;MOV AX, [[BX]] 是间接寻址,有间址);“中断周期”只在允许中断且有中断请求时发生,通常在执行周期结束后检查

3. 时间单位层级关系

CPU内部操作以时钟脉冲为基准,形成三级时间单位:

| 名称 | 定义 | 与指令周期关系 |

|---|---|---|

| 时钟周期 T | 最小时间单位,由振荡电路OSC产生,T = 1/f(f为时钟频率) | 1个机器周期 = n个时钟周期 |

| 机器周期(CPU周期) | 完成一个基本操作所需时间(如取指、访存、ALU运算),通常以主存访问时间为基准 | 1个指令周期 = 多个机器周期 |

| 指令周期 | CPU取出并执行一条指令所需的总时间 | 由多个机器周期组成 |

4. 指令流水的定义与目的

定义:将一条指令的执行过程划分为多个独立的阶段(如取指、译码、执行、访存、写回),每个阶段由专门的功能部件处理,多个指令的不同阶段并行执行。

目的:提高CPU利用率,提升吞吐率(单位时间完成指令数)。

七、中断系统概述

1. 中断系统的定义与关键术语

1 | |

💡 注意:“中断源” ≠ “中断请求”:源是设备,请求是信号;“中断响应”发生在指令周期结束时(一般在执行周期后),且需满足:IF=1,无更高优先级中断正在处理。

2. 中断与异常的区别

3. 中断 vs 异常(内中断 vs 外中断)

| 类型 | 名称 | 触发源 | 是否可屏蔽 | 典型例子 |

|---|---|---|---|---|

| 异常 | 内中断 | CPU内部执行指令时发生 | ❌ 不可屏蔽 | 除零错误、非法指令、缺页、溢出 |

| 中断 | 外中断 | 外部设备发出请求 | ✅ 可屏蔽 | 键盘输入、定时器到期、磁盘读写完成 |

异常不可屏蔽,中断可屏蔽(通过IF标志位控制),并且异常通常在指令执行过程中发生,中断一般在指令周期结束后响应

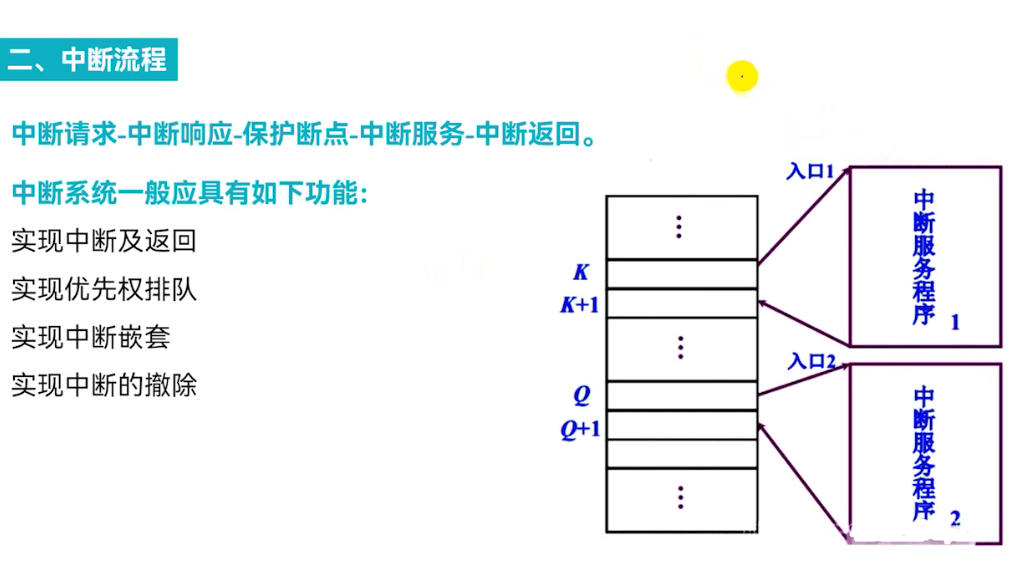

4. 中断处理流程

完整的中断处理过程如下:

1 | |

各步骤详解:

| 步骤 | 说明 |

|---|---|

| 中断请求 | 外设或异常源发出中断信号,送入CPU中断控制器 |

| 中断响应 | CPU在满足条件时(IF=1,当前指令执行完),暂停当前程序,进入中断处理 |

| 保护现场 | 将PC、PSW等寄存器内容压入栈,保存断点信息 |

| 中断服务 | 根据中断类型号查中断向量表,跳转到相应ISR执行 |

| 中断返回 | 执行IRET指令,恢复现场,返回原程序断点继续执行 |

关键机制:

中断嵌套:必须支持栈结构保存多层现场(否则会覆盖断点)。

中断撤除:在ISR结束前,需清除中断请求信号(如写EOI命令给8259A),否则会重复响应。

优先权排队:多个中断同时请求时,按优先级顺序响应(如IRQ0最高,IRQ7最低)。